# Микросхема контроллера ЛВС уровня звена данных протокола IEEE 802.3/Ethernet 5600ВГ1У, К5600ВГ1УК

ГГ – год выпуска НН – неделя выпуска

# Основные характеристики микросхемы:

- Входное напряжение от 4,5 В до 5,5 В;

- Статический ток потребления Iccs

не более 20 мА;

- Статический ток потребления (приемопередатчики в состоянии выключено) I<sub>CCS1</sub> не более 50 мкА;

- Динамический ток потребления

не более 190 мА;

- Ток короткого замыкания по выходам «TDOp» и «TDOn» 50 ÷ 100 мА;

- Время выхода в рабочий режим не более 200 мкс;

- Рабочий диапазон температур:

| Обозначение | Диапазон         |

|-------------|------------------|

| 5600ВГ1У    | минус 60 – 85 °C |

| К5600ВГ1У   | минус 60 – 85 °C |

| К5600ВГ1УК  | 0 – 70 °C        |

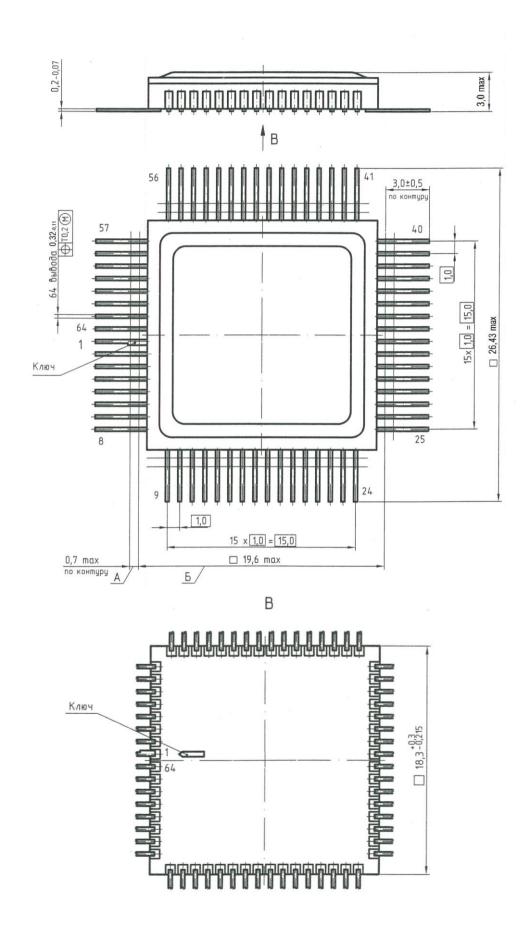

# Тип корпуса:

- 64-х выводной металлокерамический корпус Н18.64-1В.

# Общее описание и области применения микросхемы

Контроллер ЛВС предназначен для использования в устройствах локальной вычислительной сети на основе протоколов 10BASE-Т IEEE802.3/Ethernet с применением специализированных вычислительных устройств и ПК и работы под контролем управляющего устройства.

Контроллер реализует прием и передачу данных с контролем ошибок.

# Содержание

| 1 ( | Описание выводов                                                | 4  |

|-----|-----------------------------------------------------------------|----|

| 2   | Условно-графическое обозначение                                 | 7  |

|     | Структурная блок-схема микросхемы                               |    |

|     | Общее описание микросхемы                                       |    |

| 4.1 | ·                                                               |    |

| 4.2 | · ·                                                             |    |

| 4.3 |                                                                 |    |

| 4.4 |                                                                 |    |

| 4.5 | 1 1                                                             |    |

| 4.6 |                                                                 |    |

| 4.7 |                                                                 |    |

| 4.8 | ·                                                               |    |

| 4.9 |                                                                 |    |

|     | Описание функционирования микросхемы                            |    |

| 5.1 | · · · · · · · · · · · · · · · · · · ·                           |    |

| 5.2 |                                                                 |    |

| _   | 5.2.1 Параллельный порт                                         |    |

|     | 5.2.2 Последовательный порт                                     |    |

| 5.3 | ···                                                             |    |

|     | · · · · · · · · · · · · · · · · · · ·                           |    |

|     | 5.3.1 Настройка режима приема/передачи пакетов                  |    |

|     | 5.3.2 Настройка работы в полудуплексном режиме                  |    |

|     | 5.3.3 Настройка межпакетного интервала                          |    |

|     | 5.3.4 Настройка размеров пакетов                                |    |

|     | 5.3.5 Расширенные настройки передачи пакетов                    |    |

|     | 5.3.6 Контроль МАС-адреса                                       |    |

| 5.4 | 1 ''                                                            |    |

| 5.5 | · · · · · · · · · · · · · · · · · · ·                           |    |

| 5.6 | 71.                                                             |    |

| 5.7 | 11 - 1                                                          |    |

| 5.8 | 1 1                                                             |    |

| 5.9 | ' ' '                                                           |    |

| 5.1 |                                                                 |    |

|     | 5.10.1 Режим короткого замыкания (LoopBack)                     |    |

|     | 5.10.2 Отключение от линии                                      |    |

|     | Предельно-допустимые характеристики микросхемы                  |    |

|     | Электрические параметры микросхемы                              |    |

|     | Временные диаграммы                                             |    |

|     | Схема подключения                                               |    |

| 10  | Типовые зависимости                                             |    |

| 11  | Габаритный чертеж микросхемы                                    |    |

| 12  | Информация для заказа                                           |    |

|     | ЛОЖЕНИЕ 1. Регистры контроллера                                 |    |

|     | CTRL                                                            |    |

|     | AC_CTRL                                                         |    |

|     | DLLCONF                                                         |    |

|     | GTx                                                             |    |

| IN  | T_MSK/INT_SRC                                                   | 43 |

| PH  | HY_CTRL                                                         | 43 |

|     | HY_STAT                                                         | 44 |

| ST  | TAT_RX_ALL, STAT_RX_OK, STAT_RX_OVF, STAT_RX_LOST, STAT_TX_ALL, |    |

| ST  | TAT_TX_OK                                                       | 45 |

| ПРИЛОЖЕНИЕ 2. Дескриптор отсылаемых пакетовПРИЛОЖЕНИЕ 3. Дескриптор принимаемых пакетов | . 47 |

|-----------------------------------------------------------------------------------------|------|

| тт илтольний з. дескриптор принимаемых накетов                                          | 10   |

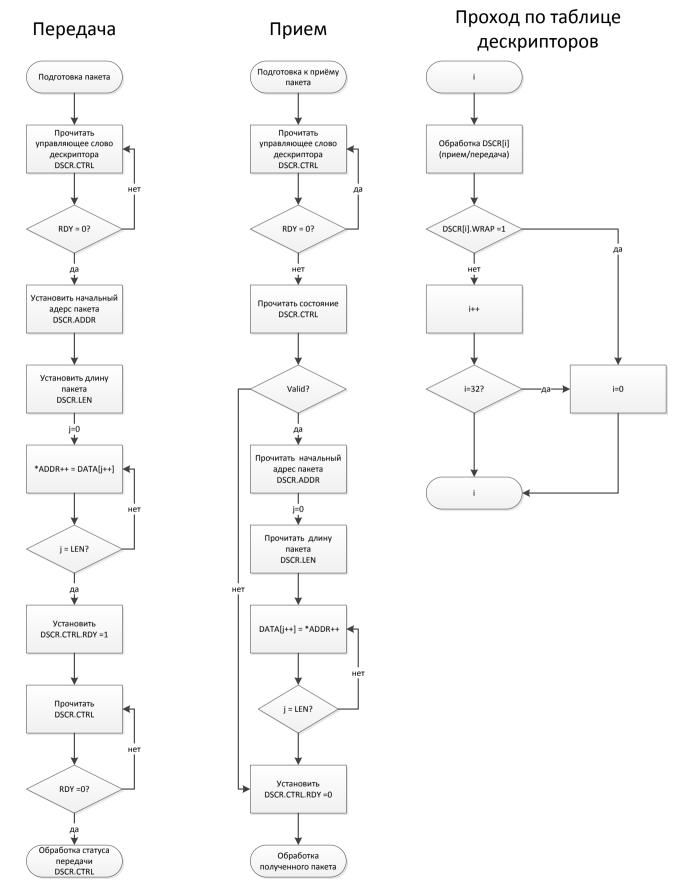

| ПРИЛОЖЕНИЕ 4. Алгоритм приема и передачи пакетов                                        | . 40 |

| ПРИЛОЖЕНИЕ 5. Драйвер (C/C++, TMS320C54x)                                               | . 49 |

| lanc_546.cmd (TMS320C546)                                                               | . 50 |

| MAC.c                                                                                   | . 50 |

| BUFF.c (TMS320C456)                                                                     | . 54 |

| MAC.h                                                                                   |      |

| MAC_types.h                                                                             | . 59 |

| ПРИЛОЖЕНИЕ 6. Фильтрация по HASH таблице                                                |      |

# 1 Описание выводов

Таблица 1 – Описание выводов микросхемы

| No se es se s    | гаолица т — описание выводов микросхемы                                                                                                                 |             |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| № вывода корпуса | Функциональное назначение выводов                                                                                                                       | Обозначение |  |  |

| 1                | Питание                                                                                                                                                 | Ucc         |  |  |

| 2                | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE                                                         | D3          |  |  |

| 3                | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE                                                         | D4          |  |  |

| 4                | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE                                                         | D5          |  |  |

| 5                | Цифровой выход данных последовательного порта.<br>В тестовом режиме сигнал TDO порта JTAG                                                               | SDO/TDO     |  |  |

| 6                | Цифровой вход данных последовательного порта.<br>В тестовом режиме сигнал TDI порта JTAG                                                                | SDI/TDI     |  |  |

| 7                | Цифровой вход. Сигнал тактовой частоты обмена по последовательному порту. В тестовом режиме сигнал ТСК порта JTAG                                       | SCLK/TCK    |  |  |

| 8                | Цифровой вход. Сигнал стробирования обмена по последовательному порту. В тестовом режиме сигнал TMS порта JTAG                                          | SFS/TMS     |  |  |

| 9                | Цифровой вход. Сигнал переключения в тестовый режим. Также сигнал nTRST порта JTAG.                                                                     | JS/nTRST    |  |  |

| 10               | Аналоговый вход кварцевого резонатора                                                                                                                   | X1          |  |  |

| 11               | Аналоговый выход кварцевого резонатора                                                                                                                  | X2          |  |  |

| 12               | Общий (аналоговый)                                                                                                                                      | GNDA        |  |  |

| 13               | Выбор режима работы от внешнего генератора или синтезатора частоты                                                                                      | XS          |  |  |

| 14               | Цифровой вход. Сброс. Активный низкий уровень                                                                                                           | nRST        |  |  |

| 15               | Цифровой выход. Запрос прерывания. Активный низкий<br>уровень.                                                                                          | nIRQ        |  |  |

| 16               | Общий                                                                                                                                                   | GND         |  |  |

| 17               | Питание                                                                                                                                                 | Ucc         |  |  |

| 18               | Цифровой вход. Сигнал выбора режима записи через параллельный порт (0 – по положительному фронту сигнала nWE; 1 – по отрицательному фронту сигнала nWE) | CLKS        |  |  |

| 19               | Цифровой вход. Сигнал рабочей частоты (управляет только снятием 3-го состояния с выхода данных в цикле чтения и формированием сигнала RDY)              | CLK         |  |  |

| 20               | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE                                                         | D6          |  |  |

| 21               | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE                                                         | D7          |  |  |

| 22               | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE                                                         | D8          |  |  |

| 23               | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE                                                         | D9          |  |  |

| 24               | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE                                                         | D10         |  |  |

| № вывода<br>корпуса | Функциональное назначение выводов                                                                              | Обозначение |

|---------------------|----------------------------------------------------------------------------------------------------------------|-------------|

| 25                  | Цифровой вход/выход двунаправленной шины данных с<br>z-состоянием. Управляется сигналами nOE и nWE             | D11         |

| 26                  | Цифровой вход/выход двунаправленной шины данных с<br>z-состоянием. Управляется сигналами nOE и nWE             | D12         |

|                     | Цифровой вход/выход двунаправленной шины данных с<br>z-состоянием. Управляется сигналами nOE и nWE             | D13         |

| 28                  | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE                | D14         |

| 29                  | Цифровой вход/выход двунаправленной шины данных с<br>z-состоянием. Управляется сигналами nOE и nWE             | D15         |

| 30                  |                                                                                                                | LED0        |

|                     | Цифровой выход индикации состояния соединения                                                                  | LED1        |

| 32                  | Общий                                                                                                          | GND         |

|                     | Питание                                                                                                        | Ucc         |

|                     | Аналоговый выход линейного интерфейса, отрицательный                                                           | TPO-        |

| 35                  | Аналоговый выход линейного интерфейса, положительный                                                           | TPO+        |

| 36                  | Аналоговый выход линейного интерфейса, отрицательный задержанный                                               | TPO         |

| 3/                  | Аналоговый выход линейного интерфейса, положительный<br>задержанный                                            | TPO++       |

| 38                  | Общий                                                                                                          | GND         |

| 39                  | Аналоговый вход линейного интерфейса, отрицательный                                                            | TPI-        |

|                     | Аналоговый вход линейного интерфейса, положительный                                                            | TPI+        |

| 41                  | Питание                                                                                                        | Ucc         |

|                     | Цифровой вход. Сигнал строба цикла обмена. Разрешает прием/передачу данных. Активный низкий уровень            | nOE         |

|                     | Цифровой вход. Сигнал записи. Управляет направлением передачи данных по шине данных. Активный низкий уровень   | nWE         |

| 44                  | Цифровой вход. Сигнал выборки кристалла. Активный низкий уровень                                               | nCS         |

|                     | Цифровой выход. Сигнал готовности. Активный высокий уровень. Выставляется по положительному фронту сигнала CLK | RDY         |

| 46                  | Цифровой вход шины адреса                                                                                      | A0          |

| 47                  | Цифровой вход шины адреса                                                                                      | A1          |

| 48                  | Общий                                                                                                          | GND         |

| 49                  | Питание                                                                                                        | Ucc         |

| 50                  | Цифровой вход шины адреса                                                                                      | A2          |

| 51                  | Цифровой вход шины адреса<br>Цифровой вход шины адреса                                                         | A3          |

| 52                  | Цифровой вход шины адреса<br>Цифровой вход шины адреса                                                         | A4          |

|                     | Цифровой вход шины адреса<br>Цифровой вход шины адреса                                                         | A5          |

| 54                  | Цифровой вход шины адреса<br>Цифровой вход шины адреса                                                         | A6          |

| 55                  | Цифровой вход шины адреса<br>Цифровой вход шины адреса                                                         | A7          |

|                     | Цифровой вход шины адреса<br>Цифровой вход шины адреса                                                         | A8          |

| 57                  | Цифровой вход шины адреса<br>Цифровой вход шины адреса                                                         | A9          |

| 58                  | цифровой вход шины адреса<br>Цифровой вход шины адреса                                                         | A9<br>A10   |

| 59                  | цифровой вход шины адреса<br>Цифровой вход шины адреса                                                         | A10         |

|                     |                                                                                                                | A11<br>A12  |

| 00                  | Цифровой вход шины адреса                                                                                      | HIZ         |

| № вывода<br>корпуса | Функциональное назначение выводов                                                               | Обозначение |

|---------------------|-------------------------------------------------------------------------------------------------|-------------|

|                     | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE | D0          |

|                     | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE | D1          |

|                     | Цифровой вход/выход двунаправленной шины данных с z-состоянием. Управляется сигналами nOE и nWE | D2          |

| 64                  | Общий                                                                                           | GND         |

# 2 Условно-графическое обозначение

| 46 |          | 5600ВГ1 | ♦ D0                                                              | 61                    |

|----|----------|---------|-------------------------------------------------------------------|-----------------------|

| 47 | A0       |         | $\stackrel{\lozenge}{\iff} \begin{array}{c} D0 \\ D1 \end{array}$ | 62                    |

| 50 | A1       |         | D1<br>D2                                                          | 63                    |

| 51 | A2       |         | D3                                                                | 2                     |

| 52 | A3       |         |                                                                   | 3                     |

| 53 | A4       |         | D4<br>D5                                                          | 4                     |

| 54 | A5       |         | D5                                                                | 20                    |

| 55 | A6       |         | D7                                                                | 21                    |

| 56 | A7<br>A8 |         | D8                                                                | 22                    |

| 57 | A9       |         | D9                                                                | 23                    |

| 58 | A10      |         | D10                                                               | 24                    |

| 59 | A11      |         | D11                                                               | 25                    |

| 60 | A12      |         | D12                                                               | 26                    |

|    | 7.12     |         | D13                                                               | 27                    |

| 44 | nCS      |         | D14                                                               | 28                    |

| 42 | nOE      |         | D15                                                               | 29                    |

| 43 | nWE      |         |                                                                   |                       |

|    | 11442    |         | RDY                                                               | 45                    |

| 19 | CLK      |         | nIRQ                                                              | 15                    |

| 18 | SCLK     |         | 111111                                                            |                       |

|    | COLIN    |         | LED0                                                              | 30                    |

| 14 | nRST     |         | LED1                                                              | 31                    |

|    |          |         |                                                                   |                       |

| 40 | TPI+     |         | TPO++                                                             | 37                    |

| 39 | TPI-     |         | TPO+                                                              | 35                    |

|    |          |         | TPO-                                                              | 34                    |

| 10 | X1       |         | TPO                                                               | 36                    |

| 11 | X2       |         |                                                                   |                       |

|    |          |         | Ucc                                                               | 1, 17, 33,<br>41, 49  |

| 13 | xs       |         | 000                                                               | 41, 49                |

|    |          |         |                                                                   |                       |

| 9  | JS/nTRST |         |                                                                   | 16 32 38              |

| 8  | SFS/TMS  |         | GND                                                               | 16, 32, 38,<br>48, 64 |

| 7  | SCLK/TCK |         |                                                                   | 12                    |

| 6  | SDI/TDI  |         | $GND_\mathtt{A}$                                                  |                       |

| 5  | SDO/TDO  |         |                                                                   |                       |

|    |          |         |                                                                   |                       |

Рисунок 1 – Условно-графическое обозначение

# 3 Структурная блок-схема микросхемы

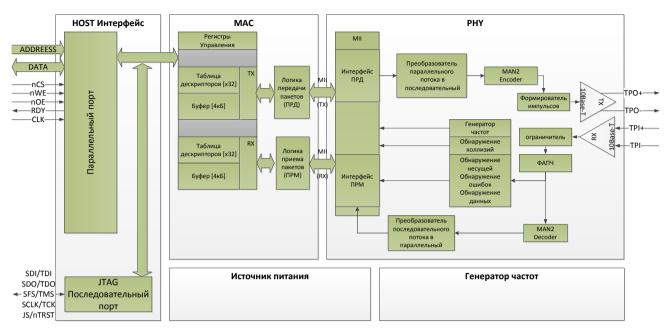

Рисунок 2 - Структурная блок-схема

# 4 Общее описание микросхемы

# 4.1 Технические характеристики

Контроллер ЛВС 5600ВГ1У (далее контроллер ЛВС) имеет один двунаправленный канал 10BASE-T IEEE 802.3/Ethernet.

В контроллере ЛВС реализованы:

- физический (PHY) уровень протокола 10BASE-T IEEE 802.3/Ethernet;

- уровень звена данных (MAC) протокола Ethernet 10BASE-T IEEE 802.3, в составе из буферов, таблиц дескрипторов, приемника и передатчика (ПРМ и ПРД соответственно):

- буферы принимаемых и передаваемых сообщений общей емкостью 8 кБ;

- параллельный интерфейс сопряжения контроллера с управляющим устройством – 16-и разрядный интерфейс с раздельными шинами адреса и данных;

- последовательный интерфейс сопряжения контроллера с управляющим устройством 4-проводный дуплексный с отдельными выводами тактового и кадрового синхросигналов;

- настройка параметров соединений в неавтоматическом режиме;

- индикация состояний соединения.

В комплект поставки микросхемы входит драйвер, предназначенный для обеспечения взаимодействия встроенного ПО управляющего устройства (далее УУ) с контроллером TMS320C50/C54x. Он предоставляет только функции и процедуры для доступа к регистрам управления, к регистрам состояния контроллера и к буферам данных.

Контроллер ЛВС предназначен для работы в среде, в которой:

- объединение узлов в ЛВС производится посредством коммутатора типа HUB на основе 5600BB2У;

- средой передачи сигнала в ЛВС является витая пара;

- настройка параметров соединений производится в неавтоматическом режиме.

# 4.2 Указания по применению и эксплуатации

При ремонте аппаратуры и измерении параметров микросхем замену микросхем необходимо проводить только при отключенных источниках питания.

Инструмент для пайки (сварки) и монтажа не должен иметь потенциал, превышающий 0,3 В относительно шины «Общий».

Запрещается подведение каких-либо электрических сигналов (в том числе шин «Питание», «Общий») к выводам микросхем, не используемым согласно схеме электрической.

Если не используется Тестовый порт вывод 9 (JS\_nTRST) необходимо подключить к шине «Общий».

Если не используется Последовательный порт вывод 7 (SCLK/TCK) необходимо подключить к шине «Общий».

Остальные выводы Последовательного/тестового порта (5, 6, 8) рекомендуется подключить к шине «Общий».

# 4.3 Регистры управления

Регистры контроллера ЛВС и их начальные значения описаны в таблице 2

Таблица 2 – Регистры управления контроллера

|              | Таолица 2 – Регистры управления контроллера |                          |                                                                                                                        |  |  |

|--------------|---------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Наименование | Номер<br>регистра                           | Значение по<br>умолчанию | Описание                                                                                                               |  |  |

| MAC_CTRL     | 0x00                                        | 0xC0A0                   | Регистр управления МАС уровнем контроллера                                                                             |  |  |

| MinFrame     | 0x01                                        | 0x0040                   | Регистр задания минимальной длины пакета                                                                               |  |  |

| MaxFrame     | 0x02                                        | 0x0600                   | Регистр задания максимальной длины<br>пакета                                                                           |  |  |

| CollConfig   | 0x03                                        | 0x0000                   | Регистр управления обработкой коллизий                                                                                 |  |  |

| IPGTx        | 0x04                                        | 0x0006                   | Регистр задания межпакетного интервала (в тактах PHY = 100ns)                                                          |  |  |

| MAC_ADDR_T   | 0x05                                        | 0x89AB                   | Регистр младшей части МАС-адреса                                                                                       |  |  |

| MAC_ADDR_M   | 0x06                                        | 0x4567                   | Регистр средней части МАС-адреса                                                                                       |  |  |

| MAC_ADDR_H   | 0x07                                        | 0x0123                   | Регистр старшей части МАС-адреса                                                                                       |  |  |

| HASH0        | 0x08                                        | 0x0000                   | Регистр слова 0 (младшего слова) HASH таблицы                                                                          |  |  |

| HASH1        | 0x09                                        | 0x0000                   | Регистр слова 1 HASH таблицы                                                                                           |  |  |

| HASH2        | 0x0A                                        | 0x0000                   | Регистр слова 2 HASH таблицы                                                                                           |  |  |

| HASH3        | 0x0B                                        | 0x8000                   | Регистр слова 3 (старшего слова) HASH таблицы                                                                          |  |  |

| INT_MSK      | 0x0C                                        | 0x0000                   | Регистр маски прерываний                                                                                               |  |  |

| INT_SRC      | 0x0D                                        | 0x0000                   | Регистр флагов прерываний                                                                                              |  |  |

| PHY_CTRL     | 0x0E                                        | 0x81D0                   | регистр управления РНҮ уровнем контроллера                                                                             |  |  |

| PHY_STAT     | 0x0F                                        | 0xXXXX                   | Регистр состояния РНҮ уровня                                                                                           |  |  |

| RXBF_HEAD    | 0x10                                        | 0x07FF                   | Регистр старшей части буфера приемника (управляется программистом и указывает на последний свободный адрес в буфере)   |  |  |

| RXBF_TAIL    | 0x11                                        | 0x0000                   | Регистр младшей части буфера приемника (управляется контроллером и указывает на первый свободный адрес в буфере)       |  |  |

| STAT_RX_ALL  | 0x14                                        | 0x0000                   | Счетчик количества входящих пакетов,<br>дошедших до МАС-уровня                                                         |  |  |

| STAT_RX_OK   | 0x15                                        | 0x0000                   | Счетчик количества успешно принятых<br>входящих пакетов (при выставленном бите<br>ERROR_FRAME_EN – считает все пакеты) |  |  |

| STAT_RX_OVF  | 0x16                                        | 0x0000                   | Счетчик количества входящих пакетов, вызвавших переполнение буфера ПРМ                                                 |  |  |

| STAT_RX_LOST | 0x17                                        | 0x0000                   | Счетчик количества входящих пакетов, потерянных из-за неготовности МАС-<br>уровня к приему (неготовность дескриптора)  |  |  |

| STAT_TX_ALL  | 0x18                                        | 0x0000                   | Счетчик количества исходящих пакетов                                                                                   |  |  |

| STAT_TX_OK   | 0x19                                        | 0x0000                   | Счетчик количества успешно отосланных исходящих пакетов                                                                |  |  |

|              | 0x120x1E                                    |                          | Зарезервировано                                                                                                        |  |  |

| GCTRL        | 0x1F                                        | 0x4382                   | Регистр управления стыка с HOST                                                                                        |  |  |

<u>Примечание</u> – Подробное описание битов регистров приведено в Приложении 1.

### 4.4 Внешние интерфейсы

Контроллер ЛВС имеет два интерфейса сопряжения с другими устройствами: параллельную шину с раздельными адресом и данными и двунаправленный последовательный порт типа SPI.

Параллельный порт представлен 13-разрядной шиной адреса и 16-разрядной шиной данных и является аналогом интерфейса TMS320 C5x/C54x.

Последовательный порт типа SPI имеет общие сигналы строба и частоты ПРМ и ПРД контроллера ЛВС. Обмен по последовательному порту осуществляется в пакетном режиме. Пакет состоит в общем случае из байта команды и её параметров. Для команд чтения и записи пакеты состоят из соответствующей команды, сопровождаемой начальным адресом и последовательностью слов данных. Для каждого последующего слова данных адрес чтения/записи инкрементируется в пределах адресного пространства контроллера. Предельная частота обмена по SPI – 20 МГц.

По сбросу контроллер ЛВС устанавливается в режим работы через параллельный порт.

Переключение между портами возможно в процессе работы контроллера только через последовательный порт. В режиме работы через последовательный порт работа через параллельный порт не доступна.

Подробное описание приведено в разделе «Интерфейс внешней шины».

#### 4.5 Адресное пространство

В контроллере ЛВС имеется встроенные независимые циклические буферы ПРМ и ПРД емкостью 2К 16-разрядных слов каждый.

Также для управления параметрами передачи в контроллере ЛВС имеются таблицы дескрипторов пакетов ПРМ и ПРД. 32 дескриптора пакетов ПРМ и 32 дескриптора пакетов ПРД (по 8 байт каждый).

|                          | 0x1FFF |

|--------------------------|--------|

|                          | 0x1FE0 |

| Регистры управления      | 0x1FDF |

|                          | 0x1FC0 |

|                          | 0x1FBF |

|                          | 0x1880 |

| Таблица дескрипторов ПРД | 0x187F |

| (32 х8 байт)             | 0x1800 |

| Буфер ПРД (4кБ)          | 0x17FF |

|                          | 0x1000 |

|                          | 0x0FFF |

|                          | 0x0880 |

| Таблица дескрипторов ПРМ | 0x087F |

| (32 х8 байт)             | 0x0800 |

| Буфер ПРМ (4кБ)          | 0x07FF |

|                          | 0x0000 |

Рисунок 3 – Карта адресного пространства 5600ВГ1У

#### Примечание:

Адресация в 16-разрядных словах.

Чтение/запись в буферы и таблицы со стороны управляющего устройства возможна одновременно с приёмом и/или передачей данных.

# 4.6 Дескрипторы

Дескрипторы предназначены для задания параметров приёма/передачи отдельных пакетов и отражения состояния приема и передачи соответственно. Для приема и передачи имеется 2 таблицы по 32 записи/дескриптора каждая. Порядок и назначение полей дескрипторов приведены в таблице 2.

Таблица 2 - Назначение полей дескрипторов

| Обозначение | Смещение | Назначение                         |

|-------------|----------|------------------------------------|

| CTRL        | 0        | поле управления и состояния пакета |

| LEN         | 1        | длина пакета                       |

| Reserved    | 2        | зарезервировано                    |

| ADDR        | 3        | адрес начала блока данных пакета   |

|               | ADDR     | 0x007F |

|---------------|----------|--------|

| Дескриптор 31 | reserved |        |

|               | LEN      |        |

|               | CTRL     | 0x007C |

. . .

|              | ADDR     | 0x0007 |

|--------------|----------|--------|

| Дескриптор 1 | reserved |        |

|              | LEN      |        |

|              | CTRL     | 0x0004 |

|              | ADDR     | 0x0003 |

| Дескриптор 0 | reserved | 0x0002 |

|              | LEN      | 0x0001 |

|              | CTRL     | 0x0000 |

Рисунок 4 – Порядок расположения дескрипторов в адресном пространстве

<u>Примечание</u> – Подробное описание полей управления дескрипторов ПРД и ПРМ приведено в Приложении 2 и Приложении 3 соответственно.

## 4.7 Ядро MAC IEEE 802.3/Ethernet

Ядро МАС контроллера ЛВС соответствует стандарту IEEE 802.3/Ethernet, и поддерживает работу в дуплексном, так и в полудуплексном режимах, включая обнаружение ошибок, обнаружение и вставку преамбулы пакета, а также вычисление, вставку и проверку контрольной суммы CRC.

Регистры управления позволяют производить гибкую настройку режима работы, управлять параметрами приёма/передачи, дополнять пакеты до минимальной длины (по стандарту IEEE 802.3).

## 4.8 Физический уровень (РНҮ)

В контроллер ЛВС встроен модуль физического уровня (РНҮ) протокола IEEE802.3/Ethernet. Данный модуль включает кодер и декодер кода Манчестер-2, ФАПЧ, автоматический фазовый детектор.

Контроллер ЛВС производит обнаружение наличия подключения к линии и формирование сигналов присутствия на линии и имеет аналоговые приёмопередающие каскады для упрощённого подключения к линии при помощи трансформаторных развязок.

Данный модуль предназначен для работы по стандарту 10BASE-Т и обеспечивает скорость подключения до 10 Мбит/с.

## 4.9 Драйвер

Программное обеспечение (драйвер) предназначено для предоставления программисту средств управления контроллером. Драйвер включает в себя макроопределения регистровой модели устройства, определение регистровых структур и базовые функции для приёма, отправки пакетов и проверки контроля результата их отправки. Подробное описание приведено в Приложении 5.

# 5 Описание функционирования микросхемы

Контроллер ЛВС выполняет две основные функции — прием и передачу пакетов Ethernet.

Для правильной работы контроллера ЛВС необходима предварительная настройка.

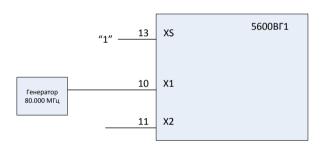

## 5.1 Тактирование

Основная рабочая частота контроллера 80 МГц. Контроллер содержит PLL с опорным синхросигналом 10 МГц от резонатора (подключение к выводам X1 и X2) или 80 МГц от генератора (режим обхода, подключение в выводу X1). Режим работы определяется выводом XS («1» в режиме обхода):

- Для перевода микросхемы в режим обхода на вывод XS подается высокий уровень, при этом на вход X1 подается тактовая частота 80 МГц.

- Для перевода микросхемы в режим умножения на вывод XS подается низкий уровень. При этом микросхема должна получать опорную частоту 10 МГц. В качестве источника опорной частоты может выступать кварцевый резонатор (на выводах X1 и X2) или генератор (см. Рисунок 5). В случае применения 10 МГц генератора, он должен быть подключен к входу X1 через емкость 1...10 нФ.

Режим обхода

15 пФ 10 X1 X2 Режим умножения с внешним

кварцевым резонатором

Рисунок 5 – Схемы включения внешних источников тактирования

# 5.2 Интерфейс внешней шины

Интерфейс внешней шины предназначен для связи контроллера ЛВС с внешним устройством управления (далее по тексту УУ), являющегося также источником данных. Интерфейс внешней шины состоит из двух компонентов: параллельного и последовательного портов.

В процессе работы контроллера возможно переключение на работу по последовательному порту и обратно подачей соответствующей команды управления через последовательный порт.

По сбросу контроллер ЛВС устанавливается в режим работы через параллельный порт.

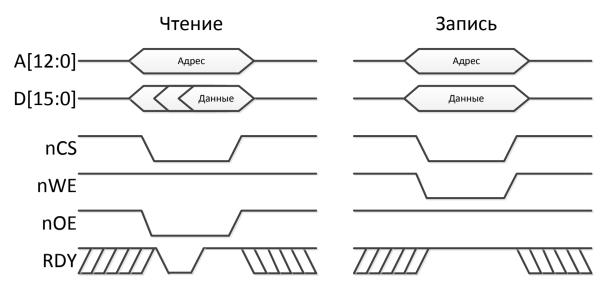

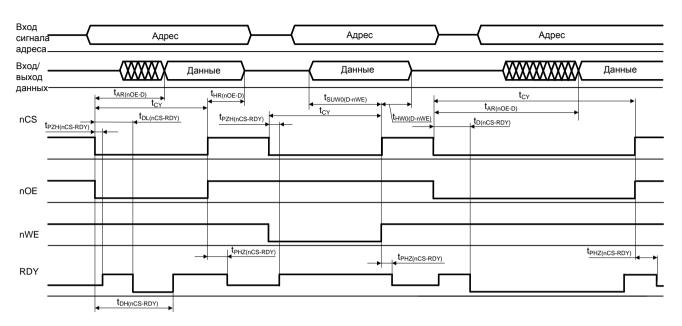

#### 5.2.1 Параллельный порт

Параллельный порт является основным средством взаимодействия с УУ. Он представлен раздельными 13-разрядной шиной адреса, 16-разрядной шиной данных и шиной управления. Параллельный порт имеет интерфейс доступа к памяти из 3-х сигналов:

- выборки устройства (nCS);

- строба чтения (nOE);

- сигнала записи (nWE).

Контроллер формирует сигнал RDY для обмена с асинхронными устройствами.

В контроллере 5600ВГ1У имеется два основных режима работы, различающихся способом выставления сигнала RDY, управляемых через внешний контакт CLKS или битом ASYNC\_MODE регистра GCTRL. В обоих режимах данные захватываются по завершении цикла обмена (нарастающему фронту сигнала nWE). Чтение начинается после выставления сигнала nOE при активном уровне сигнала nCS и неактивном уровне сигнала nWE. Сигнал RDY информирует о готовности данных при чтении или готовности принять данные при записи (внутренний цикл записи инициируется после завершения цикла — снятие управляющих сигналов).

**B режиме 1** (CLKS = 0 и ASYNC\_MODE = 0) сигнал RDY выставляется синхронно по внешнему сигналу CLK.

**В режиме 2** (CLKS = 1 или ASYNC\_MODE = 1) сигнал RDY выставляется по внутреннему тактовому сигналу асинхронно внешнему сигналу CLK.

Таблица 3 содержит перечень, тип и назначение выводов контроллера ЛВС, обеспечивающих подключение к внешней шине.

Таблица 3 – Назначение выводов интерфейса параллельного порта

| Наименование | Направление | Описание                                       |

|--------------|-------------|------------------------------------------------|

| CLK          |             | Вход тактовой частоты                          |

| A[12 – 0]    |             | 13-разрядная параллельная шина адреса          |

| D[15 – 0]    | I/O         | 16-разрядная параллельная шина данных          |

| nOE          | I           | Разрешение чтения                              |

|              |             | 0 – чтение                                     |

|              |             | 1 – неактивное состояние выводов D             |

| nWE          | I           | Разрешение записи                              |

|              |             | 0 – запись                                     |

|              |             | 1 – чтение                                     |

| nCS          | I           | Сигнал выборки ИМС                             |

|              |             | 0 – выбрана                                    |

|              |             | 1 – не выбрана, неактивное состояние выводов D |

| RDY          | 0           | Сигнал готовности                              |

|              |             | 0 – цикл не завершен                           |

|              |             | 1 – цикл завершен                              |

| nIRQ         | 0           | Сигнал запроса прерывания (активный уровень    |

|              |             | «O»)                                           |

| nRST         |             | Сигнал сброса (активный уровень «0»)           |

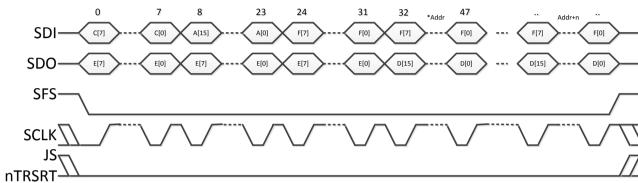

#### Рисунок 6 - Диаграммы чтения/записи параллельного порта

#### Примечания:

- 1. Не допускаются блочные транзакции (без снятия сигналов nCS, nWE и nOE/nRE).

- 2. Рекомендуется использовать длительности цикла обмена не менее 125 нс.

- 3. Не рекомендуется использовать частоту работы внешней шины выше 40 МГц.

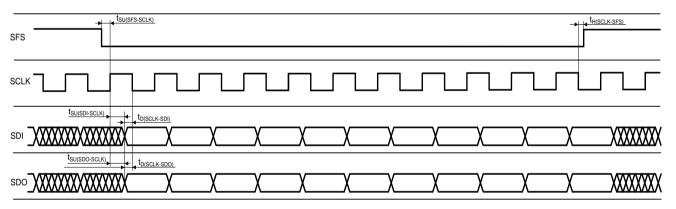

#### 5.2.2 Последовательный порт

Последовательный порт является вспомогательным и предназначен для использования в схемах с малоинтенсивным обменом и с ограниченными возможностями по подключению с УУ.

Таблица 4 содержит перечень, тип и назначение выводов контроллера ЛВС, обеспечивающих подключение к внешней шине.

| Наименование | Направление | Описание         |

|--------------|-------------|------------------|

| SFS          | I           | Строб кадра ПРД  |

| SDO          | 0           | Выход данных ПРД |

| SCLK         | I           | Вход частоты ПРД |

| SDI          | I           | Вход данных ПРМ  |

Таблица 4 – Назначение выводов интерфейса последовательного порта

Неактивный уровень строба данных («1») приводит к прерыванию чтения/записи. По фронту сигнала SCLK данные меняются, по срезу сигнала SCLK данные фиксируются.

Обращение через последовательный порт осуществляется в пакетном режиме. Пакет (кадр) представляет собой последовательность байт и его размер определяется сигналом SFS. Все время передачи кадра сигнал SFS должен удерживаться в «0». Между передачей кадров сигнал SFS устанавливаться в «1». Размер пакета определяется числом полных переданных байт в период низкого уровня SFS.

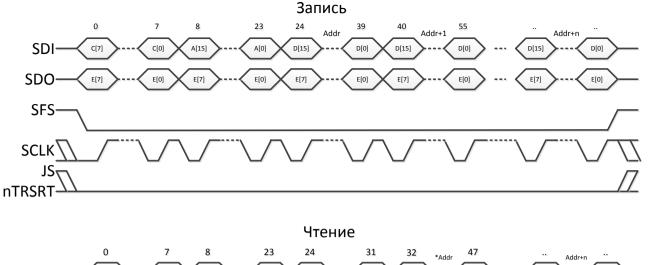

Рисунок 7 – Диаграммы чтения/записи последовательного порта

С[7..0] – код команды;

А[15..0] – начальный адрес (для команд записи/чтения);

D[15..0] – данные (для команд записи/чтения);

F[7..0] – заполнитель на время приёма данных (0x00);

**E**[7..0] – код ошибки

Таблица 5 - Описание команд

| Наименование Значение |             | Описание                                 |  |  |  |  |

|-----------------------|-------------|------------------------------------------|--|--|--|--|

| Cmd_RESET             | 0xFF        | Сброс устройства                         |  |  |  |  |

| Cmd_selectSPI         | 0x18        | Режим работы через последовательный порт |  |  |  |  |

| Cmd_selectPPI         | 0x24        | Режим работы через параллельный порт     |  |  |  |  |

| Cmd_Write             | 0x3C        | Запись блока данных                      |  |  |  |  |

| Cmd_Read 0x42         |             | Чтение блока данных                      |  |  |  |  |

|                       | Коды ошибок |                                          |  |  |  |  |

| NoErr                 | 0x00        | Нет ошибок                               |  |  |  |  |

| ErrCMD                | 0x01        | Неверный/неизвестный код команды         |  |  |  |  |

Порядок следования бит: первый бит MSB.

Порядок следования байтов: старший байт первый.

Примечание – При чтении данных выдаваемые данные задерживаются на 1байт.

Команда чтения/записи считывает/записывает данные последовательно слово за словом вне зависимости от региона памяти, в который попадает адрес операции (буфер ПРМ, буфер ПРД, таблицы дескрипторов и т.д.).

При чтении данных из буфера данных ПРМ программист должен контролировать адрес операции и количество считываемых слов, чтобы избежать чтения данных из-за пределов буфера данных ПРМ.

Аналогичная процедура выполняется для операций записи буфера данных ПРМ и операций чтения/записи буфера данных ПРД.

Характеристики порта:

- независимые ПРМ и ПРД;

- скорость обмена до 20 Мбит/с.

# 5.3 Настройка контроллера

Настройка контроллера ЛВС необходима для правильной работы ПРМ и ПРД. Настройка контроллера может осуществляться в любое время — как сразу после завершения процедуры сброса, так и в процессе работы контроллера ЛВС. Часть настроек выполняется автоматически внутренними схемами управления и обеспечивает базовые параметры для осуществления приема и передачи пакетов. Для правильной работы контроллера требуется произвести дополнительные настройки.

По сбросу устанавливаются основные, часто используемые, настройки ПРМ и ПРД. ПРМ и ПРД после сброса выключены. Минимально необходимые действия по настройке включают указание МАС адреса контроллера ЛВС, настройка маски прерываний, включение ПРМ/ПРД.

#### 5.3.1 Настройка режима приема/передачи пакетов

Устройство может работать в дуплексном или полудуплексном режимах на скорости передачи до 10 Мбит/с. По сбросу контроллер устанавливается в дуплексный режим работы.

#### 5.3.2 Настройка работы в полудуплексном режиме

Полудуплексный режим работы контроллера включается установкой бита HALFD\_EN=1 регистра MAC\_CTRL. В этом режиме осуществляется контроль занятости линии (CRS) и коллизий (COL) не осуществляется.

В полудуплексном режиме пользователю доступны для установки следующие параметры:

- окно коллизий\*. Задаётся битами [7:0] регистра CollConfig и выражается в количестве тактов частоты TxCLK (2,5 МГц). При возникновении поздней коллизии модуль прекращает передачу пакета, выставляет состояние ошибки и переходит к обработке следующего пакета;

- количество попыток передачи пакета. Лимит количества попыток содержится в регистре CollConfig (биты [15:8]). Если количество коллизий, произошедших во время передачи пакетов, превышает значение этого регистра, модуль прекращает передачу пакета, выставляет состояние ошибки и переходит к обработке следующего пакета.

#### Примечание:

\* Окно коллизий – это время t после начала отправки пакета (в соответствии со спецификацией IEEE 802.3), по прошествии которого любая произошедшая коллизия считается поздней.

#### 5.3.3 Настройка межпакетного интервала

Значение длины межпакетного интервала, выраженное в битовых интервалах (100 нс), заносится в регистр IPGTx. После отправки пакета передатчик блокирует обработку следующего дескриптора на заданное время.

#### 5.3.4 Настройка размеров пакетов

Максимальный и минимальный размер пакета содержится в регистрах MaxFrame и MinFrame соответственно (в байтах).

Если размер пакета, передаваемый модулем, (в байтах) меньше значения регистра MinFrame, передатчик, если разрешено (бит PAD\_DIS=0), дополняет поле данных пакета нулевыми байтами.

Количество нулевых байт N вычисляется как:

- 1) N = значение регистра MinFrame (байт) L (длина пакета, содержащаяся в поле длины дескриптора), если CRC DIS = 1;

- 2) N = значение регистра MinFrame (байт) L (длина пакета, содержащаяся в поле длины дескриптора) 4, если CRC DIS = 0.

Если принимаемый пакет содержит количество байт больше значения, содержащегося в регистре MaxFrame, то приемник записывает в текущий дескриптор состояние ошибки и переходит к следующему дескриптору.

#### 5.3.5 Расширенные настройки передачи пакетов

Контроллер ЛВС предоставляет возможность расширенного управления отправкой пакетов через поле управления дескриптора передачи.

Передаваемый пакет можно конфигурировать следующим образом:

- разрешить или запретить автоматическое добавление поля CRC в конец пакета (бит CRC\_DIS дескриптора отсылаемых пакетов);

- разрешить или запретить автоматическое добавление нулевых бит к полям данных пакетов, имеющих длину поля данных меньше минимальной (бит PAD DIS дескриптора отсылаемых пакетов).

#### 5.3.6 Контроль МАС-адреса

Модуль МАС осуществляет автоматический контроль адреса назначения принимаемого пакета. Доступны следующие режимы фильтрации пакетов:

- прием всех пакетов;

- прием индивидуального пакета;

- прием широковещательных пакетов;

- прием пакетов по HASH таблице.

Режим «без фильтрации» (приём всех пакетов) осуществляется включением бита PRO EN регистра MAC CTRL.

Приём индивидуального пакета включен всегда и осуществляется по полному совпадению принятого в пакете MAC-адреса со значением, установленным в качестве MAC-адреса контроллера в регистрах MAC\_ADDR\_x.

Прием широковещательного пакета осуществляется при приеме пакета с широковещательным MAC-адресом независимо от остальных режимов при включенном бите BCA EN регистра MAC CTRL.

Прием пакетов по HASH таблице осуществляется, если HASH-функция MAC-адреса принятого пакета соответствует маске в HASH-таблице контроллера. HASH-функция MAC-адреса вычисляется как «1» в позиции за номером, равным числу в старших 6 разрядах CRC32 MAC-адреса назначения (см. Приложение 6).

HASHTAG = 1 << ((CRC32(MAC))>> 26);

Режим работает независимо от остальных и включается битом MCA\_EN регистра MAC\_CTRL.

#### 5.4 Передача пакетов

Передача пакетов в контроллере ЛВС производится в 4 этапа:

1 этап: Копирование данных пакета УУ в буфер ПРД контроллера.

**2 этап:** Установка параметров передачи пакета записью соответствующих параметров в дескриптор ПРД пакета (см. приложение 2):

- формирование или нет прерываний по завершении обработки пакета (бит IRQ\_EN);

- добавление или нет преамбулы (бит PRE DIS);

- дополнение или нет пакета PAD-символами ( $0\times00$ ) до минимальной длины (бит PAD DIS);

- дополнение или нет пакета полем CRC (бит CRC\_DIS).

**3 этап:** Определение МАС-модулем по дескриптору пакета параметров передачи и собственно передача пакета. Передача включает автоматическую установку прочих параметров пакета, дополнение коротких пакетов до необходимой длины, расчет и вставка СRC, отработка временных интервалов при передаче пакетов, повторную отправку пакетов в случае ошибки при отправке.

**4 этап:** Формирование статусной информации о передаче, куда включаются признаки завершения обработки пакета (бит RDY), количество попыток отправки (поле RTRY), признак отказа от передачи из-за превышения лимита попыток (бит RL), признака ошибки в линии (бит LC). Также при разрешенных прерываниях передатчика выставляются прерывания завершения обработки пакета (бит TXF), наличия ошибок в пакете (бит TXE), передача пакета управления (бит TXC) и занятость передатчика по причине обслуживания контрольного пакета PAUSE (бит TX BUSY).

По завершении передачи контроллер переходит к обработке очередного дескриптора из таблицы, согласно биту WRAP. При достижении конца таблицы производится переход к ее началу, независимо от бита WRAP последнего дескриптора.

<u>Примечание</u> – Бит RDY поля управления дескриптора должен устанавливаться последним(!).

Общий алгоритм передачи одиночного пакета приведен в Приложении 4.

## 5.5 Прием пакетов

Прием пакетов, как и передача, осуществляется в 4 этапа:

**1 этап:** Настройка дескриптора ПРМ (см. Приложение 3), которая заключается в установке признаков готовности дескриптора к обработке (бит RDY) и в установке признака разрешения формирования прерывания по завершении приема (бит IRQ\_EN).

**2 этап:** Прием данных пакета. При приеме контролируются ошибки приема, и анализируется прочая информация, такая как МАС-адрес, с целью определения необходимости фиксации пакета в памяти и формировании статусной информации о приеме.

3 этап: Запись статусной информации в дескриптор:

- тип МАС-адреса принятого пакета;

- групповой пакет, прошедший проверку через HASH таблицу (бит MCA);

- широковещательный пакет (бит ВСА);

- пакет с индивидуальным MAC-адресом (бит UCA);

- параметры пакета;

- пакет управления (бит CF);

- пакет длиной более MaxFrame (бит LF);

- пакет длиной менее MinFrame (бит SF);

- наличия ошибок при приёме пакета (бит EF);

- типы ошибок при приёме (если таковые были);

- несоответствие расчётного CRC пакета содержимому поля CRC (бит CRC\_ERR);

- наличие ошибки в теле пакета (бит SMB ERR);

- наличие ошибки типа LateCollision (бит LC);

- наличие переполнения буфера ПРМ при приёме пакета (бит OR).

#### А также выставляются прерывания:

- завершения приема пакета (бит RXF);

- приема пакета с ошибками (бит RXE);

- прием пакета длиной более MaxFrame (бит RXL);

- прием пакета длиной менее MinFrame (бит RXS);

- прием пакета управления (бит RXC);

- переполнение буфера приёмника (бит RXBF FULL);

- поступление пакета при неготовности текущего дескриптора (бит RXD\_nREADY).

**4 этап:** По получении информации о приеме пакета (через бит занятости дескриптора или через прерывание), осуществляется считывание УУ пакета из памяти контроллера ЛВС.

По завершении передачи контроллер переходит к обработке очередного дескриптора из таблицы, согласно биту WRAP. При достижении конца таблицы производится переход к её началу, независимо от бита WRAP последнего дескриптора.

<u>Примечание</u> – Общий алгоритм приема одиночного пакета приведен в Приложении 4.

# 5.6 Работа РНҮ уровня

Модуль PHY контроллера ЛВС это одноканальный приемопередатчик протокола стандарта IEEE 802.3/Ethernet 10BASE-T, предоставляющий все функции протокола физического уровня.

Управление модулем осуществляется через регистры управления, находящиеся в общем пуле регистров.

Блок осуществляет контроль наличия коллизий в линии в полудуплексном режиме работы, а также осуществляет функции слежения за подключением к линии по наличию передачи или импульсов LINK и формирования импульсных посылок LINK для индикации присутствия на линии. При превышении времени отсутствия изменений в линии блок формирует сигнал отсутствия подключения.

#### 5.7 Индикация

В контроллере 5600ВГ1 предусмотрены выводы для индикации состояния при помощи внешних светодиодов.

Управление индикацией осуществляется через два вывода LED0 и LED1. Назначение выводов и их состояния приведены ниже (Таблица 6).

Частота мерцания индикаторов – 5 Гц.

Таблица 6 – Назначение и состояния выводов при индикации

| Индикатор | Состояние | Назначение                      |  |  |

|-----------|-----------|---------------------------------|--|--|

| LED0      | 0         | Полудуплексный режим работы     |  |  |

| LED0      | 1         | Дуплексный режим работы         |  |  |

| LED0      | 0→1→0→    | Наличие коллизии в линии        |  |  |

| LED1      | 0         | Соединение с линией             |  |  |

| LED1      | 1         | Отсутствует соединение с линией |  |  |

| LED1      | 0→1→0→    | Производится обмен пакетами     |  |  |

## 5.8 Прерывания

За обработку прерываний отвечают два регистра:

- регистр флагов прерываний;

- регистр маски прерываний.

Прерывания блокируются записью «0» в регистр маски прерываний.

При возникновении прерывания вывод INT устанавливается в низкий уровень. Вывод INT устанавливается в высокий уровень после очистки регистра флагов прерываний. Очистка регистра флагов прерываний осуществляется его чтением (при установленном бите GCTRL.READ\_CLR\_STAT) или записью «1» в соответствующий разряд регистра флагов INT SRC.

Подробное описание флагов прерываний описано в Приложении 1.

# 5.9 Работа драйвера

Программное обеспечение (драйвер) предназначено для предоставления программисту средств управления контроллером. Драйвер включает в себя макроопределения регистровой модели устройства, определение регистровых структур и базовые функции для приема, отправки пакетов данных и проверки контроля результата их отправки.

Предоставляемая в драйвере процедура инициализации предназначена для инициализации контроллера ЛВС значениями, отличными от значений по умолчанию.

Предоставляемые функции отправки и приема пакета реализуют также и настройку соответствующего дескриптора по флагам, установленным в аргументах соответствующих функций.

Исходный код драйвера приведен в Приложении 5.

## 5.10 Особенности работы контроллера в разных режимах

#### 5.10.1 Режим короткого замыкания (LoopBack)

Режим короткого замыкания (далее КЗ) предназначен для проведения проверок работы программно-аппаратной части устройства в пределах самого устройства без подключения к линии.

В контроллере ЛВС реализовано два способа организации режима КЗ:

- цифровое КЗ:

- аналоговое КЗ.

Цифровое КЗ предназначено для организации обратной петли на стыке MAC и PHY уровней. Режим устанавливается выставлением бита LB\_EN регистра MAC\_CTRL или выставлением бита DLB регистра PHY CTRL.

Аналоговое КЗ служит для проверки работы и настройки всего контроллера в целом до подключения к линии. Режим устанавливается выставлением бита LB регистра PHY\_CTRL.

#### 5.10.2 Отключение от линии

Контроллер 5600ВГ1 может быть отключен от линии, как на прием, так и на передачу независимо друг от друга. Данный режим может быть использован при самотестировании работы контроллера программными средствами без нарушения работы линии. Включение и отключение ПРМ и ПРД осуществляется битами RXEN и TXEN соответственно (1 – включено, 0 – отключено). После сброса (программного или аппаратного) приемник и передатчик переводятся в неактивное состояние.

Отключение затрагивает только выходные каскады и не влияет на работу остальной части схемы. Таким образом, для работы в режиме КЗ нет необходимости в присутствии на линии прочих устройств.

# 6 Предельно-допустимые характеристики микросхемы

Таблица 7 – Предельно-допустимые и предельные режимы эксплуатации микросхем

|                                                                                                                                                 | a z                                       | Норма параметра                   |       |                     |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------|-------|---------------------|-----------|

| Наименование параметра режима,<br>единица измерения                                                                                             | Буквенное<br>обозначени<br>е              | Предельно-<br>допустимый<br>режим |       | Предельный<br>режим |           |

|                                                                                                                                                 | 5y<br>60                                  | не                                | не    | не                  | не        |

|                                                                                                                                                 |                                           | менее                             | более | менее               | более     |

| Напряжение питания, В                                                                                                                           | Ucc                                       | 4,5                               | 5,5   | _                   | 6,0       |

| Входное напряжение низкого уровня, В, на выводах A[12:0], D[15:0], nCS, nOE, nWE, CLK, CLKS, nRST, JS_nTRST, SFS/TMS, SCLK/TCK, SDI/TDI, XS, X1 | UıL                                       | 0                                 | 0,8   | минус 0,3           | -         |

| Входное напряжение высокого уровня, В, на выводе XS и X1 при XS=1                                                                               | Uıн                                       | 0, <b>7∙</b> Ucc                  | Ucc   | _                   | Ucc +0,3  |

| Входное напряжение высокого уровня, В, на выводах A[12:0], D[15:0], nCS, nOE, nWE, CLK, CLKS, nRST, JS_nTRST, SFS/TMS, SCLK/TCK, SDI/TDI        | Uıн                                       | 2,4                               | Ucc   | _                   | Ucc +0,3  |

| Дифференциальное входное напряжение на выводах TPI+ и TPI-, мВ                                                                                  | U <sub>IT</sub>                           | 500                               | Ucc   | _                   | _         |

| Входное напряжение на выводах TPI+ и<br>TPI-, В                                                                                                 | Uı                                        | _                                 | _     | минус 0,3           | Ucc + 0,3 |

| Ток нагрузки на цифровых выходах, мА,<br>D[15:0], RDY, nIRQ, LED[1:0], SDO/TDO,<br>X2                                                           | Iol<br>Ioн                                | минус<br>4,0                      | 4,0   | минус<br>10,0       | 10,0      |

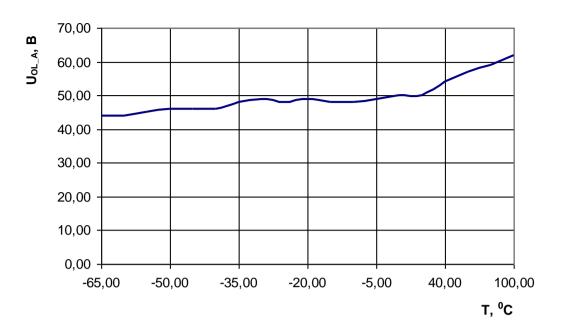

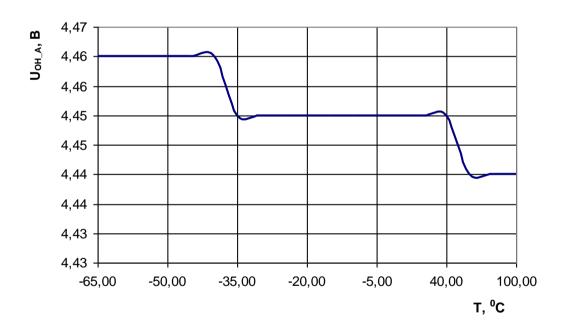

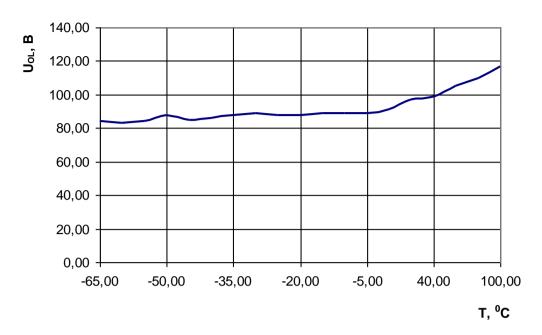

| Ток нагрузки на аналоговых выходах ТРО++, ТРО+, ТРО, ТРО, мА                                                                                    | I <sub>OL_A</sub><br>I <sub>OH_A</sub>    | минус<br>40,0                     | 40,0  | минус<br>80,0       | 80,0      |

| Частота следования импульсов тактовых сигналов, МГц, - в режиме обхода XS=1                                                                     | fc                                        | _                                 | 80    | -                   | -         |

| - в режиме умножения частоты XS=0                                                                                                               |                                           | _                                 | 10    | _                   | -         |

| Частота следования импульсов тактовых сигналов параллельного интерфейса, МГц, на выводе CLK                                                     | fcLĸ*                                     | _                                 | 40    | _                   | -         |

| Частота следования импульсов тактовых сигналов последовательного интерфейса, МГц, на выводе SCLK/TCK                                            | fsclk/Tck*                                | _                                 | 10    | _                   | -         |

| Время нарастания и спада входного тактового сигнала, нс                                                                                         | t <sub>r_PLL</sub> * t <sub>f_PLL</sub> * | _                                 | 3     | _                   | _         |

| Минимальная длительность сигнала<br>сброса, нс                                                                                                  | tmclr*                                    | 100                               | _     | _                   | _         |

| Емкость нагрузки на выходах, пф                                                                                                                 | CL                                        | _                                 | 60    | _                   | _         |

#### Примечания:

<sup>1.\*</sup>Временные параметры fc, fclk, fsclk/тck, tr\_Pll, tf\_Pll, tmclr гарантируются в процессе проведения ФК на максимальной частоте.

<sup>2.</sup> Не допускается одновременное задание нескольких предельных режимов.

# 7 Электрические параметры микросхемы

Таблица 8 – Электрические параметры микросхем при приёмке и поставке

| Наименование параметра,<br>единица измерения,                                                                                             | Буквенное<br>обозначение<br>параметра | Норма<br>параметра |             | Температура<br>среды, °С |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------|-------------|--------------------------|

| режим измерения                                                                                                                           | Букво<br>обозна<br>параг              | не<br>менее        | не<br>более | Температ<br>среды,       |

| Выходное напряжение низкого уровня на<br>цифровых выходах D[15:0], RDY, nIRQ,<br>LED[1:0], SDO/TDO, B                                     | UoL                                   | _                  | 0,4         | 25,<br>85,<br>минус 60   |

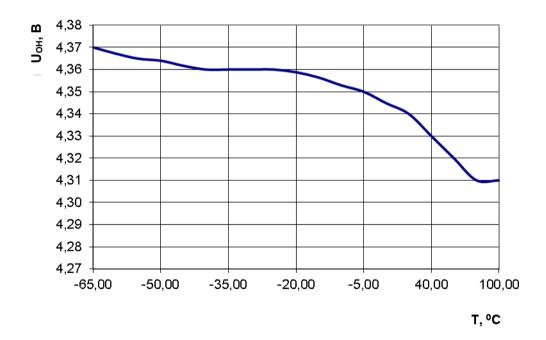

| Выходное напряжение высокого уровня на<br>цифровых выходах D[15:0], RDY, nIRQ,<br>LED[1:0], SDO/TDO, B                                    | Uон                                   | 4,05               | -           | 25,<br>85,<br>минус 60   |

| Выходное напряжение низкого уровня на<br>аналоговых выходах ТРО++, ТРО+, ТРО,<br>ТРО, X2, В                                               | Uol_a                                 | _                  | 1,1         | 25,<br>85,<br>минус 60   |

| Выходное напряжение высокого уровня на<br>аналоговых выходах TPO++, TPO+, TPO,<br>TPO, X2, B                                              | Uон_а                                 | 3,5                | -           | 25,<br>85,<br>минус 60   |

| Ток утечки низкого уровня на цифровых входах A[12:0], D[15:0], nCS, nOE, nWE, CLK, CLKS, nRST, JS_nTRST, SFS/TMS, SCLK/TCK, SDI/TDI, мкА  | I <sub>ILL</sub>                      | минус<br>1,0       | 1,0         | 25,<br>85,<br>минус 60   |

| Ток утечки высокого уровня на цифровых входах A[12:0], D[15:0], nCS, nOE, nWE, CLK, CLKS, nRST, JS_nTRST, SFS/TMS, SCLK/TCK, SDI/TDI, мкА | Іігн                                  | минус<br>1,0       | 1,0         | 25,<br>85,<br>минус 60   |

| Входной ток низкого уровня на аналоговых входах TPI+, TPI-, X1, мА                                                                        | I <sub>IL_</sub> A                    | минус<br>1,0       | 1,0         | 25,<br>85,<br>минус 60   |

| Входной ток высокого уровня на аналоговых входах TPI+, TPI-, X1, мА                                                                       | Іін_а                                 | минус<br>1,0       | 1,0         | 25,<br>85,<br>минус 60   |

| Ток утечки низкого уровня на входе XS (13), мкА                                                                                           | I <sub>ILL_</sub> xs                  | минус<br>50        | 50          | 25,<br>85,<br>минус 60   |

| Ток утечки высокого уровня на входе XS (13), мкА                                                                                          | IILH_XS                               | минус<br>50        | 50          | 25,<br>85,<br>минус 60   |

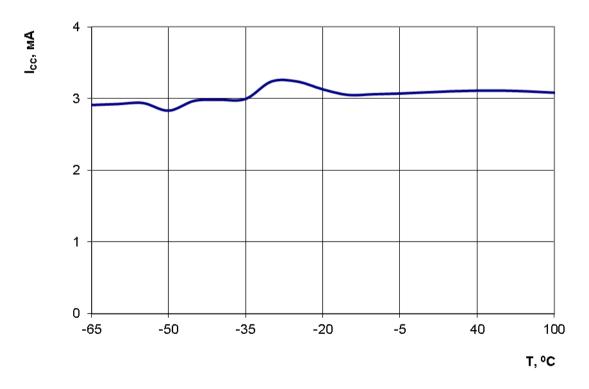

| Статический ток потребления, мА                                                                                                           | Icc                                   | _                  | 20          | 25,<br>85,<br>минус 60   |

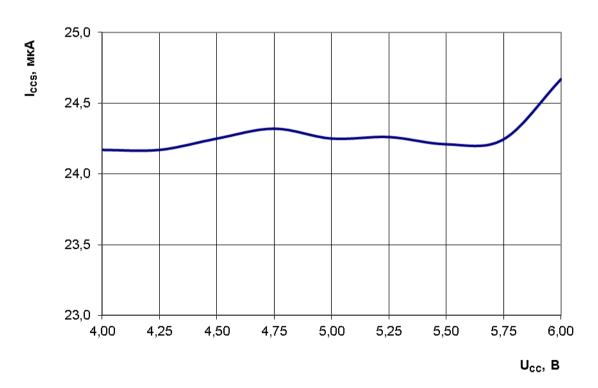

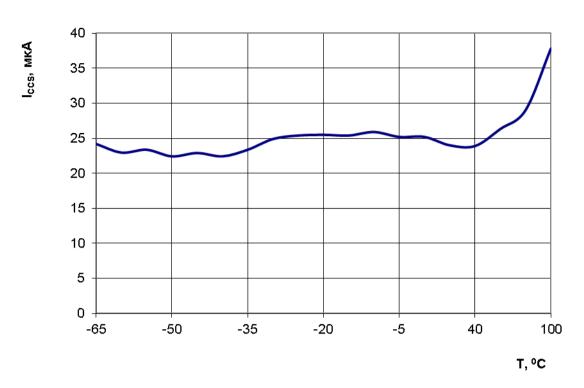

| Статический ток потребления (приемопередатчики в состоянии «Выключено»), мкА                                                              | Iccs                                  | _                  | 50          | 25,<br>85,<br>минус 60   |

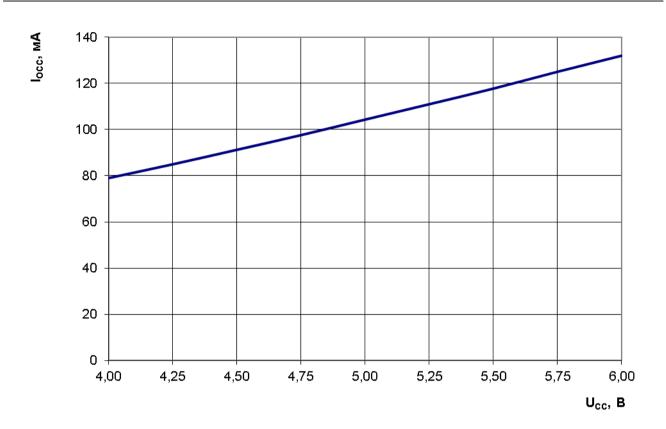

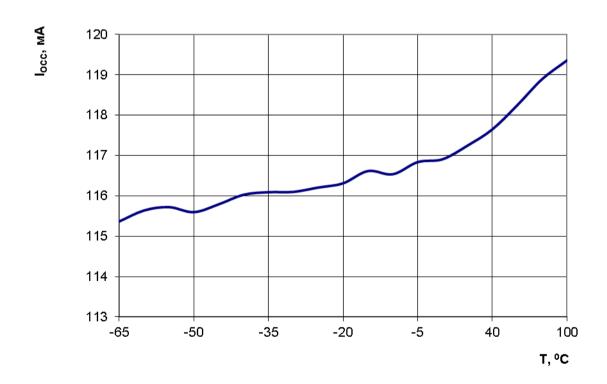

| Динамический ток потребления, мА                                                                                                          | locc                                  | _                  | 190         | 25,<br>85,<br>минус 60   |

| Наименование параметра,                                                                                                                    | Буквенное<br>обозначение<br>параметра | Норма<br>параметра |             | оатура<br>ы, °С          |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------|-------------|--------------------------|

| единица измерения,<br>режим измерения                                                                                                      | Буквенное<br>обозначени<br>параметра  | не<br>менее        | не<br>более | Температура<br>среды, °С |

| Выходная частота генератора, МГц                                                                                                           | fo_PLL*                               | 79,9               | 80,1        | 25,<br>85,<br>минус 60   |

| Параметры параллельного интерфейса                                                                                                         |                                       |                    | •           |                          |

| Время цикла чтения/записи, нс                                                                                                              | tcy*                                  | 100                | -           | 25,<br>85,<br>минус 60   |

| Время задержки при переходе выхода RDY из состояния «Выключено» в состояние высокого (низкого) уровня относительно сигнала nCS, нс         | tPZH(nCS-RDY)* tPZL(nCS-RDY)*         | -                  | 12,5        | 25,<br>85,<br>минус 60   |

| Время задержки сигнала RDY при переходе выхода из состояния высокого (низкого) уровня в состояние «Выключено» относительно сигнала nCS, нс | tPHZ(nCS-RDY)* tPLZ (nCS-RDY)*        | -                  | 12,5        | 25,<br>85,<br>минус 60   |

| Время задержки установки сигнала RDY<br>относительно сигнала nCS, нс                                                                       | tDH(nCS-RDY)*                         | 87,5               | _           | 25,<br>85,<br>минус 60   |

| Время задержки снятия сигнала RDY относительно nCS, нс, при: CLKS=0                                                                        | t <sub>DL(nCS-RDY)</sub> *            | _                  | H**         | 25,<br>85,               |

| при: CLKS=1                                                                                                                                |                                       | _                  | 12,5        | минус 60                 |

| Время выборки данных относительно сигнала nOE, в цикле чтения, нс                                                                          | tAR(nOE-D)*                           | -                  | 112,5       | 25,<br>85,<br>минус 60   |

| Время удержания данных относительно<br>сигнала nOE, в цикле чтения, нс                                                                     | tHR(nOE-D)*                           | 12,5               | _           | 25,<br>85,<br>минус 60   |

| Время предустановки данных относительно начала сигнала разрешения записи nWE, в цикле записи, нс при: CLKS=0                               | tsuwo(D-nWE)*                         | 12,5               | _           | 25,<br>85,<br>минус 60   |

| Время удержания данных относительно сигнала разрешения записи nWE, в цикле записи, нс при: CLKS=0                                          | tHW0(nWE-D)*                          | 12,5               | _           | 25,<br>85,<br>минус 60   |

| Параметры последовательного интерфейса                                                                                                     |                                       |                    |             |                          |

| Время задержки сигнала SDI (SDO) относительно SCLK, нс                                                                                     | td(sclk-sdi)* td(sclk-sdo)*           | 12,5               | _           | 25,<br>85,<br>минус 60   |

| Время предустановки сигнала SFS<br>относительно сигнала SCLK, нс                                                                           | tsu(SFS-SCLK)*                        | 12,5               | _           | 25,<br>85,<br>минус 60   |

| Время предустановки данных относительно<br>сигнала SCLK, нс                                                                                | tsu(sdi-sclk)* tsu(sdo-sclk)*         | 12,5               | _           | 25,<br>85,<br>минус 60   |

| Наименование параметра,                                      | енное<br>ачение<br>метра | Норма<br>параметра |             | ература<br>ды, °С      |  |

|--------------------------------------------------------------|--------------------------|--------------------|-------------|------------------------|--|

| единица измерения,<br>режим измерения                        | Букве<br>обозна<br>парал | не<br>менее        | не<br>более | Темпер                 |  |

| Время удержания сигнала SFS относительно<br>сигнала SCLK, нс | th(sclk-sfs)*            | 12,5               | _           | 25,<br>85,<br>минус 60 |  |

#### Примечания:

2.\*\*H=1/2•fcLK

<sup>1. \*</sup>Временные параметры fo\_pll, tcy, tpzh(ncs-rdy), tpzl(ncs-rdy), tphz(ncs-rdy), tplz (ncs-rdy), tdh(ncs-rdy), tdl(ncs-rdy), tar(noe-d), thr(noe-d), tsuwo(d-nwe), thwo(nwe-d), td(sclk-sdi), td(sclk-sdo), tsu(sps-sclk), tsu(sdi-sclk), tsu(sdo-sclk), th(sclk-sfs) гарантируются в процессе проведения ФК на максимальной частоте.

# 8 Временные диаграммы

Рисунок 8 – Временная диаграмма циклов чтения и записи параллельного интерфейса при: CLKS=0, CLKS=1

Рисунок 9 – Временная диаграмма циклов чтения и записи последовательного интерфейса

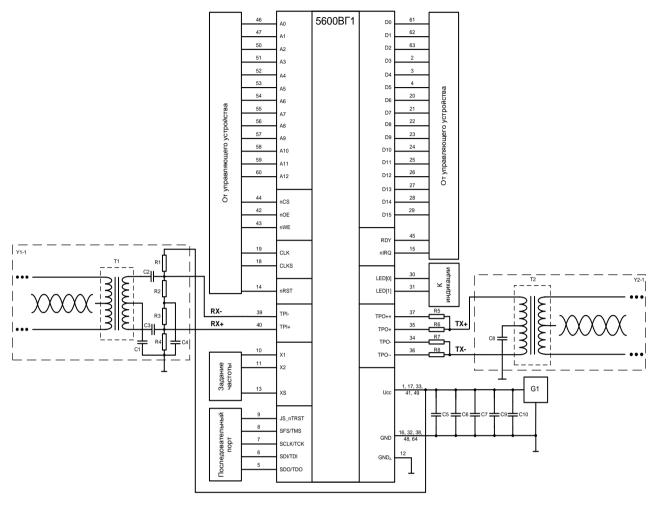

# 9 Схема подключения

5600ВГ1 – включаемая микросхема;

G2 — источник постоянного напряжения,  $U_{CC} = 5.0 B$ ;

R1 - R8 — сопротивления;

Для линии с волновым сопротивлением 100 Ом:

R1 = R4 = 1  $\kappa$ Om\*  $\pm$  5 %, 0,25 BT;

$R2 = R3 = 50 \text{ Om } \pm 5 \%, 0.25 \text{ BT};$

$R5 = R8 = 390 \text{ Om } \pm 5 \%, 0.25 \text{ BT};$

$R6 = R7 = 47 \text{ Om } \pm 5 \%, 0.25 \text{ Bt.}$

Для линии с волновым сопротивлением 75 Ом:

R1 = R4 = 1  $\kappa$ Om\*  $\pm$  5 %, 0,25 BT;

$R2 = R3 = 36 \text{ Om } \pm 5 \%, 0.25 \text{ BT};$

$R5 = R8 = 270 \text{ Om } \pm 5 \%, 0.25 \text{ BT};$

$R6 = R7 = 36 \text{ Om } \pm 5 \%, 0,25 \text{ Bt.}$

Рисунок 10 – Схема реализации устройства на базе одной микросхемы

#### Продолжение к рисунку 10

```

С1–С9 — конденсаторы;

С1 = C4 = C5 = C6 = C7 = C8 = C9 = C10 = 0,1 мкФ \pm 10 %;

С2 = C3 = не более 33 мкФ и не менее 33 нФ.

Т1, Т2 — трансформаторы, L = 350 мкГн, 1:1;

Y1 — элементы схемы (Y1-1; — Y1-2).

```

\* – Резисторы R1 и R4 могут не устанавливаться, при этом не гарантируется прием LINK-импульсов и, как следствие, – невозможность определения подключения или отключения линии.

Номиналы резисторов подбираются согласно волновому сопротивлению провода и равны 1/2 • R провода.

# 10 Справочные данные

Максимальное значение емкости вывода микросхемы на частотах менее 1 МГц не превышает 9 пФ.

Таблица 9 – Справочные параметры

| Наименование параметра,                                                  | квенное<br>значение<br>раметра         | Нор<br>парам | атура<br>ı, °C |                        |

|--------------------------------------------------------------------------|----------------------------------------|--------------|----------------|------------------------|

| единица измерения,<br>режим измерения                                    | Буквенное<br>обозначение<br>параметра  | не менее     | не более       | Температ<br>среды,     |

| Входное сопротивление приемника, кОм по выводам                          | R <sub>I_RCV</sub>                     | 5            | 18             | 25,<br>85,<br>минус 60 |

| Длительность сигнала высокого уровня (импульса LINK), нс, при Ucc= 4,5 В | t <sub>WHWT</sub>                      | 100          | _              | 25,<br>85,<br>минус 60 |